# 25-common x 100-segment BITMAP LCD DRIVER

# ■ GENERAL DESCRIPTION

The **NJU6673** is a 25-common x 100-segment bit map LCD driver to display graphics or characters.

It contains 2,500 bits display data RAM, microprocessor interface circuits, instruction decoder, and common and segment drivers.

An image data from MPU through the serial or 8-bit parallel interface are stored into the 2,500 bits internal displayed on the LCD panel through the commons and segments drivers.

The **NJU6673** displays 25 x 100 dots graphics or 7-character 2-line by  $12 \times 13$  dots character.

The **NJU6673** contains a built-in OSC circuit for reducing external components. And it features an electrical variable resistor. As result, it reduces the operating current.

The operating voltage from 2.4V to 5.5V and low operating current are suitable for small size battery operation items.

# **FEATURES**

- Direct Correspondence of Display Data RAM to LCD Pixel

- Display Data RAM 2,500 bits

- LCD Drivers 25-common and 100-segment

- Selectable Duty and Bias Ratio ; 1/25 Duty 1/6 Bias or 1/15 Duty 1/5 Bias

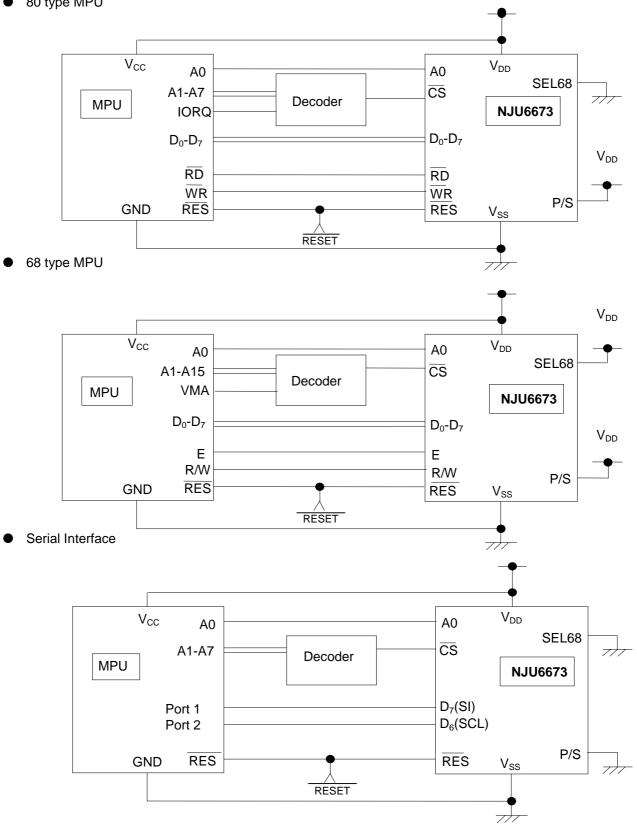

- Direct connection to 8-bit Microprocessor interface for both of 68 and 80 type MPU

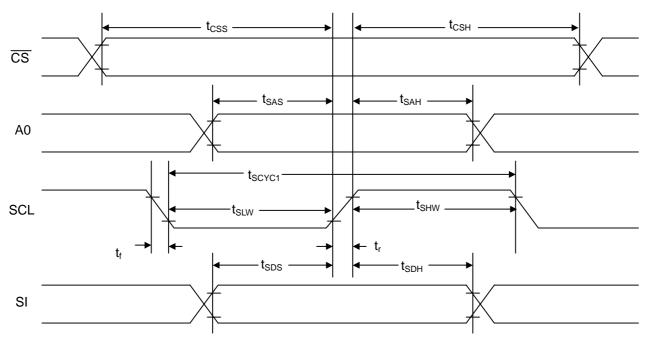

- Serial Interface (SI, SCL, A0,  $\overline{CS}$ )

- Useful instruction set Display ON/OFF, Display Start Line Set, Page Address Set, Column Address Set, Status Read, Write Display Data, Read Display Data, Normal or Inverse ON/OFF Set, Static Drive ON/Normal Display, EVR Register Set, Read Modify Write, End, Reset, Internal Power Supply ON/OFF, Driver Output ON/OFF, Power Save and ADC select.

- Power Supply Circuits for LCD; Available attractive operation for small LCD panel without external capacitors for bias stabilization. Booster Circuits(3 times maximum, Voltage boosting polarity : Negative (V<sub>DD</sub> Common)), Regulator, Voltage Follower(x 4)

- Precision Electrical Variable Resistance (16 Steps)

- Low Power Consumption

- Operating Voltage 2.4V to 5.5V

- LCD Driving Voltage 4.0V to 10.0V

- Package Outline Bumped Chip

- C-MOS Technology (Substrate : N)

NJU6673CL

PACKAGE OUTLINE

# NJU6673

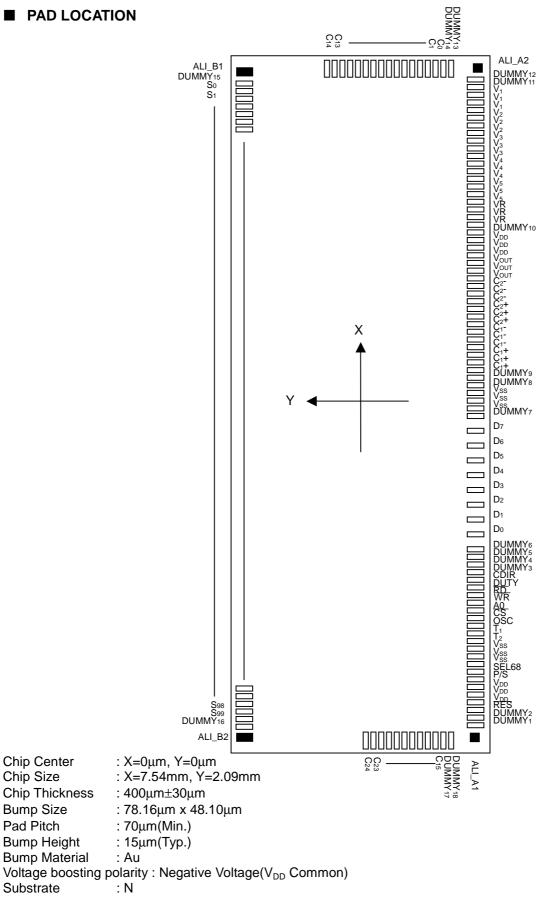

PAD LOCATION

# ■ TERMINAL DESCRIPTION

|         | Torrainal            | V     |       |         |                       |             | Y=0μm) |

|---------|----------------------|-------|-------|---------|-----------------------|-------------|--------|

| PAD No. | Terminal             | X= μm | Y= μm | PAD No. | Terminal              | $X = \mu m$ | Y= μm  |

| 1       | DUMMY <sub>1</sub>   | -3536 | -891  | 51      | V <sub>OUT</sub>      | 1715        | -891   |

| 2       | DUMMY <sub>2</sub>   | -3466 | -891  | 52      | V <sub>OUT</sub>      | 1786        | -891   |

| 3       | RES                  | -3396 | -891  | 53      | V <sub>OUT</sub>      | 1856        | -891   |

| 4       | V <sub>DD</sub>      | -3326 | -891  | 54      | V <sub>DD</sub>       | 1926        | -891   |

| 5       | V <sub>DD</sub>      | -3256 | -891  | 55      | V <sub>DD</sub>       | 1996        | -891   |

| 6       | V <sub>DD</sub>      | -3186 | -891  | 56      | V <sub>DD</sub>       | 2066        | -891   |

| 7       | P/S                  | -3116 | -891  | 57      | DUMMY <sub>10</sub>   | 2136        | -891   |

| 8       | SEL68                | -3046 | -891  | 58      | VR                    | 2206        | -891   |

| 9       | V <sub>SS</sub>      | -2976 | -891  | 59      | VR                    | 2276        | -891   |

| 10      | V <sub>SS</sub>      | -2906 | -891  | 60      | VR                    | 2346        | -891   |

| 11      | V <sub>SS</sub>      | -2836 | -891  | 61      | V <sub>5</sub>        | 2416        | -891   |

| 12      | T2                   | -2766 | -891  | 62      | V <sub>5</sub>        | 2486        | -891   |

| 13      | T1                   | -2696 | -891  | 63      | V <sub>5</sub>        | 2556        | -891   |

| 14      | OSC <sub>1</sub>     | -2626 | -891  | 64      | V <sub>4</sub>        | 2626        | -891   |

| 15      | CS                   | -2556 | -891  | 65      | V <sub>4</sub>        | 2696        | -891   |

| 16      | A0                   | -2486 | -891  | 66      | V <sub>4</sub>        | 2766        | -891   |

| 17      | WR                   | -2416 | -891  | 67      | V <sub>3</sub>        | 2836        | -891   |

| 18      | RD                   | -2346 | -891  | 68      | V <sub>3</sub>        | 2906        | -891   |

| 19      | DUTY                 | -2276 | -891  | 69      | V <sub>3</sub>        | 2976        | -891   |

| 20      | CDIR                 | -2206 | -891  | 70      | V <sub>2</sub>        | 3046        | -891   |

| 21      | DUMMY <sub>3</sub>   | -2136 | -891  | 71      | V <sub>2</sub>        | 3116        | -891   |

| 22      | DUMMY <sub>4</sub>   | -2066 | -891  | 72      | V <sub>2</sub>        | 3186        | -891   |

| 23      | DUMMY <sub>5</sub>   | -1996 | -891  | 73      | V <sub>1</sub>        | 3256        | -891   |

| 24      |                      | -1926 | -891  | 74      | V <sub>1</sub>        | 3326        | -891   |

| 25      | D <sub>0</sub>       | -1715 | -891  | 75      | V <sub>1</sub>        | 3396        | -891   |

| 26      | D <sub>1</sub>       | -1435 | -891  | 76      | DUMMY <sub>11</sub>   | 3466        | -891   |

| 27      | D <sub>2</sub>       | -1155 | -891  | 77      | DUMMY <sub>12</sub>   | 3536        | -891   |

| 28      | D <sub>3</sub>       | -875  | -891  | 78      | ALI_A2                | 3616        | -891   |

| 29      | D <sub>4</sub>       | -595  | -891  | 79      | DUMMY <sub>13</sub>   | 3616        | -745   |

| 30      | D <sub>5</sub>       | -315  | -891  | 80      | DUMMY <sub>14</sub>   | 3616        | -675   |

| 31      | D <sub>6</sub> (SCL) | -35   | -891  | 81      | C <sub>0</sub>        | 3616        | -605   |

| 32      | D <sub>7</sub> (SI)  | 245   | -891  | 82      | C <sub>1</sub>        | 3616        | -535   |

| 33      | DUMMY <sub>7</sub>   | 455   | -891  | 83      | C <sub>2</sub>        | 3616        | -465   |

| 34      | V <sub>SS</sub>      | 525   | -891  | 84      | C <sub>3</sub>        | 3616        | -395   |

| 35      | V <sub>SS</sub>      | 595   | -891  | 85      | C <sub>4</sub>        | 3616        | -325   |

| 36      | V <sub>SS</sub>      | 665   | -891  | 86      | C <sub>5</sub>        | 3616        | -255   |

| 37      | DUMMY <sub>8</sub>   | 735   | -891  | 87      | C <sub>6</sub>        | 3616        | -185   |

| 38      | DUMMY <sub>9</sub>   | 805   | -891  | 88      | C <sub>7</sub>        | 3616        | -115   |

| 39      | C1 <sup>+</sup>      | 875   | -891  | 89      | C <sub>8</sub>        | 3616        | -45    |

| 40      | C1 <sup>+</sup>      | 945   | -891  | 90      | C <sub>9</sub>        | 3616        | 25     |

| 41      | C1 <sup>+</sup>      | 1015  | -891  | 91      | C <sub>10</sub>       | 3616        | 95     |

| 42      | C1 <sup>-</sup>      | 1085  | -891  | 92      | C <sub>10</sub>       | 3616        | 166    |

| 43      | C1 <sup>-</sup>      | 1155  | -891  | 93      | C <sub>12</sub>       | 3616        | 236    |

| 44      | C1 <sup>-</sup>      | 1225  | -891  | 94      | C <sub>13</sub>       | 3616        | 306    |

| 45      | C2 <sup>+</sup>      | 1295  | -891  | 95      | C <sub>14</sub>       | 3616        | 376    |

| 46      | C2 <sup>+</sup>      | 1365  | -891  | 96      | ALI_B1                | 3616        | 873    |

| 47      | C2 <sup>+</sup>      | 1435  | -891  | 97      | DUMMY <sub>15</sub>   | 3536        | 891    |

| 48      | C2 <sup>-</sup>      | 1505  | -891  | 98      | <b>S</b> <sub>0</sub> | 3466        | 891    |

| 49      | C2 <sup>-</sup>      | 1575  | -891  | 99      | S <sub>1</sub>        | 3396        | 891    |

| 50      | C2 <sup>-</sup>      | 1645  | -891  | 100     | S <sub>2</sub>        | 3326        | 891    |

New Japan Radio Co.,Ltd. -

| PAD No. | Terminal                           | X= μm      | Y= μm      | PAD No. | Terminal                           | X= μm | Y= μm      |

|---------|------------------------------------|------------|------------|---------|------------------------------------|-------|------------|

| 101     | S <sub>3</sub>                     | 3256       | 891        | 151     | S <sub>53</sub>                    | -245  | 891        |

| 102     | S <sub>4</sub>                     | 3186       | 891        | 152     | S <sub>54</sub>                    | -315  | 891        |

| 103     | S <sub>5</sub>                     | 3116       | 891        | 153     | S <sub>55</sub>                    | -385  | 891        |

| 104     | S <sub>6</sub>                     | 3046       | 891        | 154     | S <sub>56</sub>                    | -455  | 891        |

| 105     | S <sub>7</sub>                     | 2976       | 891        | 155     | S <sub>57</sub>                    | -525  | 891        |

| 106     | S <sub>8</sub>                     | 2906       | 891        | 156     | S <sub>58</sub>                    | -595  | 891        |

| 107     | S <sub>9</sub>                     | 2836       | 891        | 157     | S <sub>59</sub>                    | -665  | 891        |

| 108     | S <sub>10</sub>                    | 2766       | 891        | 158     | S <sub>60</sub>                    | -735  | 891        |

| 109     | S <sub>11</sub>                    | 2696       | 891        | 159     | S <sub>61</sub>                    | -805  | 891        |

| 110     | S <sub>12</sub>                    | 2626       | 891        | 160     | S <sub>62</sub>                    | -875  | 891        |

| 111     | S <sub>13</sub>                    | 2556       | 891        | 161     | S <sub>63</sub>                    | -945  | 891        |

| 112     | S <sub>14</sub>                    | 2486       | 891        | 162     | S <sub>64</sub>                    | -1015 | 891        |

| 113     | S <sub>15</sub>                    | 2416       | 891        | 163     | S <sub>65</sub>                    | -1085 | 891        |

| 114     | S <sub>16</sub>                    | 2346       | 891        | 164     | S <sub>66</sub>                    | -1155 | 891        |

| 115     | S <sub>17</sub>                    | 2276       | 891        | 165     | S <sub>67</sub>                    | -1225 | 891        |

| 116     | S <sub>18</sub>                    | 2206       | 891        | 166     | S <sub>68</sub>                    | -1295 | 891        |

| 117     | S <sub>19</sub>                    | 2136       | 891        | 167     | S <sub>69</sub>                    | -1365 | 891        |

| 118     | S <sub>20</sub>                    | 2066       | 891        | 168     | S <sub>70</sub>                    | -1435 | 891        |

| 119     | S <sub>21</sub>                    | 1996       | 891        | 169     | S <sub>71</sub>                    | -1505 | 891        |

| 120     | S <sub>22</sub>                    | 1926       | 891        | 170     | S <sub>72</sub>                    | -1575 | 891        |

| 121     | S <sub>23</sub>                    | 1856       | 891        | 171     | S <sub>73</sub>                    | -1645 | 891        |

| 122     | S <sub>24</sub>                    | 1786       | 891        | 172     | S <sub>74</sub>                    | -1715 | 891        |

| 123     | S <sub>25</sub>                    | 1700       | 891        | 172     | S <sub>75</sub>                    | -1786 | 891        |

| 120     | S <sub>26</sub>                    | 1645       | 891        | 176     | S <sub>76</sub>                    | -1856 | 891        |

| 125     | S <sub>27</sub>                    | 1575       | 891        | 175     | S <sub>77</sub>                    | -1926 | 891        |

| 125     | S <sub>27</sub>                    | 1505       | 891        | 176     | S <sub>77</sub>                    | -1996 | 891        |

| 120     | S <sub>28</sub><br>S <sub>29</sub> | 1435       | 891        | 170     | S <sub>78</sub>                    | -2066 | 891        |

| 127     | S <sub>29</sub><br>S <sub>30</sub> | 1365       | 891        | 178     | S <sub>79</sub><br>S <sub>80</sub> | -2000 | 891        |

| 120     | S <sub>30</sub><br>S <sub>31</sub> | 1295       | 891        | 179     | S <sub>80</sub>                    | -2206 | 891        |

| 130     | S <sub>31</sub>                    | 1235       | 891        | 180     | S <sub>81</sub>                    | -2276 | 891        |

| 130     | S <sub>32</sub>                    | 1155       | 891        | 181     | S <sub>82</sub><br>S <sub>83</sub> | -2346 | 891        |

| 131     | S <sub>33</sub><br>S <sub>34</sub> | 1085       | 891        | 182     | S <sub>83</sub><br>S <sub>84</sub> | -2416 | 891        |

| 132     | S <sub>34</sub>                    | 1005       | 891        | 183     | S <sub>84</sub>                    | -2486 | 891        |

| 133     | 035<br>C                           | 945        | 891        | 183     | S <sub>85</sub><br>S <sub>86</sub> | -2480 | 891        |

| 134     | S <sub>36</sub>                    | 945<br>875 | 891        | 185     |                                    | -2626 | 891        |

| 135     | S <sub>37</sub><br>S <sub>38</sub> | 805        | 891        | 186     | S <sub>87</sub><br>S <sub>88</sub> | -2696 | 891        |

| 130     | S <sub>38</sub><br>S <sub>39</sub> | 735        | 891        | 187     | S <sub>88</sub><br>S <sub>89</sub> | -2696 | 891        |

| 137     | S <sub>39</sub><br>S <sub>40</sub> | 665        | 891        | 187     | S <sub>89</sub><br>S <sub>90</sub> | -2766 | 891        |

|         |                                    |            |            |         |                                    |       | 891        |

| 139     | S <sub>41</sub>                    | 595<br>525 | 891<br>801 | 189     | S <sub>91</sub>                    | -2906 |            |

| 140     | S <sub>42</sub>                    | 525        | 891<br>801 | 190     | S <sub>92</sub>                    | -2976 | 891<br>801 |

| 141     | S <sub>43</sub>                    | 455        | 891<br>801 | 191     | S <sub>93</sub>                    | -3046 | 891        |

| 142     | S <sub>44</sub>                    | 385        | 891        | 192     | S <sub>94</sub>                    | -3116 | 891        |

| 143     | S <sub>45</sub>                    | 315        | 891        | 193     | S <sub>95</sub>                    | -3186 | 891        |

| 144     | S <sub>46</sub>                    | 245        | 891        | 194     | S <sub>96</sub>                    | -3256 | 891        |

| 145     | S <sub>47</sub>                    | 175        | 891        | 195     | S <sub>97</sub>                    | -3326 | 891        |

| 146     | S <sub>48</sub>                    | 105        | 891        | 196     | S <sub>98</sub>                    | -3396 | 891        |

| 147     | S <sub>49</sub>                    | 35         | 891        | 197     | S <sub>99</sub>                    | -3466 | 891        |

| 148     | S <sub>50</sub>                    | -35        | 891        | 198     | DUMMY <sub>16</sub>                | -3536 | 891        |

| 149     | S <sub>51</sub>                    | -105       | 891        | 199     | ALI_B2                             | -3616 | 873        |

| 150     | S <sub>52</sub>                    | -175       | 891        | 200     | C <sub>24</sub>                    | -3616 | 25         |

New Japan Radio Co., Ltd.

| PAD No. | Terminal            | X= μm | Y= μm |

|---------|---------------------|-------|-------|

| 201     | C <sub>23</sub>     | -3616 | -45   |

| 202     | C <sub>22</sub>     | -3616 | -115  |

| 203     | C <sub>21</sub>     | -3616 | -185  |

| 204     | C <sub>20</sub>     | -3616 | -255  |

| 205     | C <sub>19</sub>     | -3616 | -325  |

| 206     | C <sub>18</sub>     | -3616 | -395  |

| 207     | C <sub>17</sub>     | -3616 | -465  |

| 208     | C <sub>16</sub>     | -3616 | -535  |

| 209     | C <sub>15</sub>     | -3616 | -605  |

| 210     | DUMMY <sub>17</sub> | -3616 | -675  |

| 211     | DUMMY <sub>18</sub> | -3616 | -745  |

| 212     | ALI_A1              | -3616 | -891  |

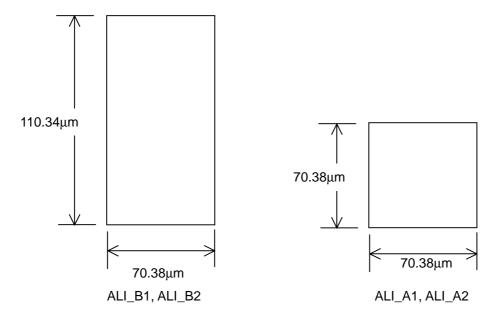

Alignment marks

Note) Alignment Marks are not contains window.

# NJU6673

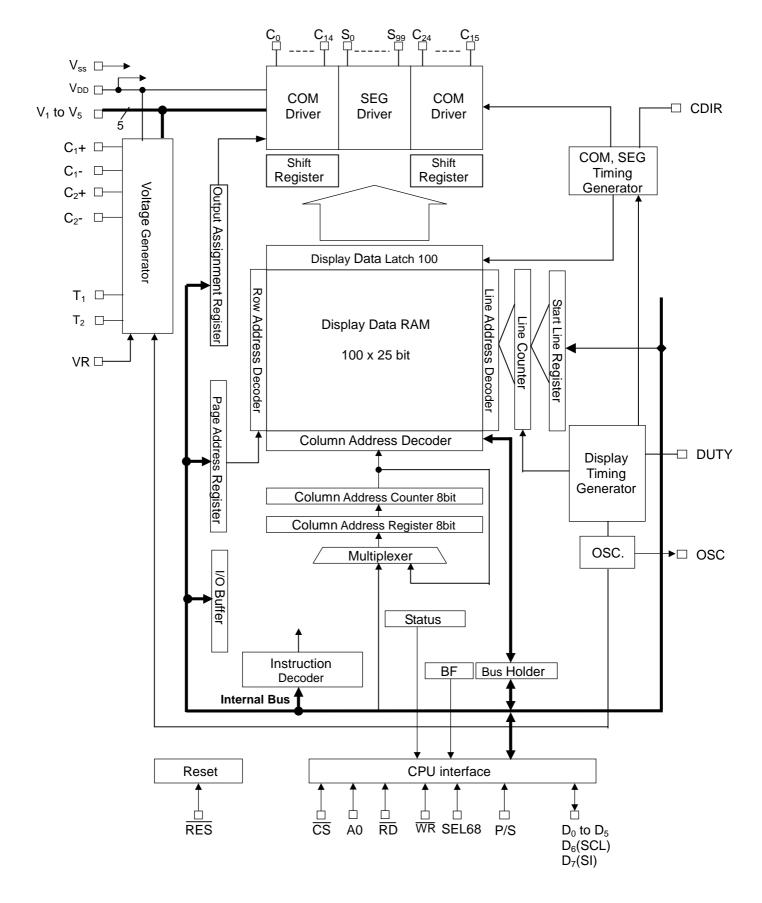

# BLOCK DIAGRAM

■ TERMINAL DESCRIPTION

| No.            | Symbol                           | I/O      | Function                                                                                               |  |  |  |  |

|----------------|----------------------------------|----------|--------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1,             | DUMMY <sub>1</sub>               |          | Dummy Terminal.                                                                                        |  |  |  |  |

| 2,             | DUMMY <sub>2</sub>               |          | These are open terminals electrically.                                                                 |  |  |  |  |

| 21-            | DUMMY <sub>3</sub> -             |          | ······································                                                                 |  |  |  |  |

| 24,            | DUMMY <sub>6</sub>               |          |                                                                                                        |  |  |  |  |

| 33,            | DUMMY <sub>7</sub>               |          |                                                                                                        |  |  |  |  |

| 37,            | DUMMY <sub>8</sub>               |          |                                                                                                        |  |  |  |  |

| 38,            |                                  |          |                                                                                                        |  |  |  |  |

|                |                                  |          |                                                                                                        |  |  |  |  |

| 57,<br>76      |                                  |          |                                                                                                        |  |  |  |  |

| 76,            |                                  |          |                                                                                                        |  |  |  |  |

| 77,<br>70      | DUMMY <sub>12</sub>              |          |                                                                                                        |  |  |  |  |

| 79,            | DUMMY <sub>13</sub>              |          |                                                                                                        |  |  |  |  |

| 80,            | DUMMY <sub>14</sub>              |          |                                                                                                        |  |  |  |  |

| 97,            | DUMMY <sub>15</sub>              |          |                                                                                                        |  |  |  |  |

| 198,           | DUMMY <sub>16</sub>              |          |                                                                                                        |  |  |  |  |

| 210,           | DUMMY <sub>17</sub>              |          |                                                                                                        |  |  |  |  |

| 211            | DUMMY <sub>18</sub>              |          |                                                                                                        |  |  |  |  |

| 4,5,6,         | $V_{DD}$                         | Power    | Power supply terminal. (+2.4 to +5.5V)                                                                 |  |  |  |  |

| 54-56          |                                  |          |                                                                                                        |  |  |  |  |

| 9-11,<br>34-36 | $V_{SS}$                         | GND      | Ground terminal. (0V)                                                                                  |  |  |  |  |

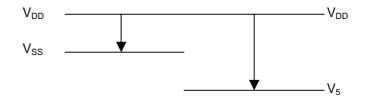

| 73-75          | V <sub>1</sub>                   |          | LCD Driving Voltage Supplying Terminals.                                                               |  |  |  |  |

| 70-72          | $V_2$                            |          | In case of external power supply operation without internal power supply                               |  |  |  |  |

| 67-69          | V <sub>2</sub><br>V <sub>3</sub> |          | operation, each level of LCD driving voltage is supplied from outside                                  |  |  |  |  |

| 64-66          | V 3<br>V4                        |          | fitting with following relation.                                                                       |  |  |  |  |

| 61-63          |                                  |          |                                                                                                        |  |  |  |  |

| 01-03          | $V_5$                            |          | $V_{DD} \ge V_1 \ge V_2 \ge V_3 \ge V_4 \ge V_5 \ge V_{OUT}$                                           |  |  |  |  |

|                |                                  | Power    | In case of internal power supply, LCD driving voltages $V_1$ to $V_4$                                  |  |  |  |  |

|                |                                  |          | depending on the bias selection are supplied as shown in follows;                                      |  |  |  |  |

|                |                                  |          | Duty Bias $V_1$ $V_2$ $V_3$ $V_4$                                                                      |  |  |  |  |

|                |                                  |          | 1/15 Duty 1/5 Bias $V_5$ +4/5 $V_{LCD}$ $V_5$ +3/5 $V_{LCD}$ $V_5$ +2/5 $V_{LCD}$ $V_5$ +1/5 $V_{LCD}$ |  |  |  |  |

|                |                                  |          | 1/25 Duty 1/6 Bias $V_5$ +5/6 $V_{LCD}$ $V_5$ +4/6 $V_{LCD}$ $V_5$ +2/6 $V_{LCD}$ $V_5$ +1/6 $V_{LCD}$ |  |  |  |  |

|                |                                  |          | V <sub>LCD</sub> =V <sub>DD</sub> -V <sub>5</sub>                                                      |  |  |  |  |

| 39-41          | C <sub>1</sub> +                 | 0        | Condenser connecting terminals for internal Voltage Booster.                                           |  |  |  |  |

| 42-44          | C <sub>1</sub> -                 |          | Boosting time is selected by each connected condenser.                                                 |  |  |  |  |

| 45-47          | C <sub>2</sub> +                 |          | 5                                                                                                      |  |  |  |  |

| 48-50          | C <sub>2</sub> -                 |          | In case of 3-time boost operation, connect the condenser between $C_1$ +                               |  |  |  |  |

|                | - 2                              |          | and $C_1$ -, $C_2$ + and $C_2$                                                                         |  |  |  |  |

|                |                                  |          | In case of 2-time boost operation, connect the condenser between $C_2$ +                               |  |  |  |  |

|                |                                  |          | and $C_2$ -, connect $C_2$ + to $C_1$ +, and $C_1$ - should be open.                                   |  |  |  |  |

| 51-53          | V <sub>OUT</sub>                 | 0        | Boosted voltage output terminal. Connects the capacitor between $V_{OUT}$                              |  |  |  |  |

| 50.00          |                                  | <u> </u> | terminal and $V_{ss}$ .                                                                                |  |  |  |  |

| 58-60          | VR                               |          | $V_{LCD}$ voltage adjustment terminal. The gain of $V_{LCD}$ setup circuit for $V_5$                   |  |  |  |  |

|                | -                                | <u> </u> | level is adjusted by external resistor.                                                                |  |  |  |  |

| 13             | Τ <sub>1</sub> ,                 |          | LCD bias voltage control terminals.                                                                    |  |  |  |  |

| 12             | T <sub>2</sub>                   |          | T <sub>1</sub> T <sub>2</sub> Voltage Voltage adjustor V/F circuit                                     |  |  |  |  |

|                |                                  |          | Booster circuit                                                                                        |  |  |  |  |

|                |                                  |          | L H/L Available Available Available                                                                    |  |  |  |  |

|                |                                  |          | H L Not available Available Available                                                                  |  |  |  |  |

|                |                                  |          | H H Not available Not available Available                                                              |  |  |  |  |

| 25             |                                  | I/O      | Data input / output torminals                                                                          |  |  |  |  |

| 25<br>26       |                                  | 1/0      | Data input / output terminals.<br>In parallel interface Mode (P/S="H")                                 |  |  |  |  |

|                | D <sub>1</sub>                   |          |                                                                                                        |  |  |  |  |

| 27             | D <sub>2</sub>                   |          | I/O terminals of 8-bit bus.                                                                            |  |  |  |  |

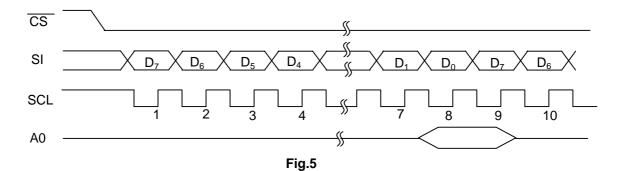

| 28             | D <sub>3</sub>                   |          | In Serial interface Mode(P/S="L")                                                                      |  |  |  |  |

| 29<br>20       | D <sub>4</sub>                   |          | $D_7$ :Input terminal of serial data (SI).                                                             |  |  |  |  |

| 30             |                                  |          | D <sub>6</sub> :Input terminal of serial data clock (SCL).                                             |  |  |  |  |

| 31<br>32       | D <sub>6</sub> (SCL)             |          | $D_5$ to $D_0$ terminals are High impedance.                                                           |  |  |  |  |

|                | D <sub>7</sub> (SI)              | 1        | When $\overline{CS}$ ="H", $D_0$ to $D_7$ terminals are high-impedance.                                |  |  |  |  |

New Japan Radio Co., Ltd. –

| No. | Symbol  | I/O | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

|-----|---------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 16  | AO      | I   | Data discremination signal input terminal.The signal from MPUdiscreminates transmitted data between Display data and Instruction.A0HDiscreminationDisplay DataInstruction                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

| 3   | RES     | I   | Reset terminal.<br>Reset operation is executing during "L" state of RES.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| 15  | CS      | I   | Chip select signal input terminal.<br>Data Input/Output are available during $CS = "L"$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

| 18  | RD (E)  | I   | <ul> <li>RD(80 type) or E(68 type) signal input terminal.</li> <li><in 80="" mode="" mpu="" type="">(SEL68="L")</in></li> <li>RD signal from 80 type MPU input terminal. Active"L".</li> <li>D<sub>0</sub> to D<sub>7</sub> terminals are output during "L" level.</li> <li><in 68="" mode="" mpu="" type="">(SEL68="H")</in></li> <li>Enable signal from 68 type MPU input terminal. Active "H"</li> </ul>                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| 17  | WR(R/W) | I   | WR (80 type) or R/W (68 type) signal input terminal. <in 80="" mode="" mpu="" type="">(SEL68="L")         WR signal from 80 type MPU input . Active "L".         The data transmitted during WR="L" are fetched at the rising edge o WR.         <in 68="" mode="" mpu="" type="">         R/w signal from 68 type MPU input terminal.         R/W       H         L         State       Read</in></in>                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| 8   | SEL68   | I   | MPU interface type selection terminal.         This terminal must connect to V <sub>DD</sub> or V <sub>SS</sub> SEL68       H         L         State       68 type         80 type                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| 7   | P/S     | Ι   | Parallel or Serial interface selection signal input terminal.         P/S       Inter face       Chip Select /Command       Data Data       Read/Write       Serial CLK         "H"       Parallel       CS       A0       D <sub>0</sub> -D <sub>7</sub> RD, WR       -         "L"       Serial       CS       A0       SI(D <sub>7</sub> )       -       SCL(D <sub>6</sub> )         In case of the serial interface (P/S="L")         RAM data and status read operation do not work in mode of the serial interface.         RD and WR terminals must fix to "H" or "L".         D to D terminals are bigh impedance. |  |  |  |  |  |  |  |

| 14  | OSC     | 0   | $D_0$ to $D_5$ terminals are high impedance.<br>Maker Testing Clock output terminal.<br>The terminal is recommended to open.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

# NJU6673

| No.     | Symbol                           | I/O | Function                                                                                                    |                                                                                                                                                                                                                                                                                                 |                                   |                                  |    |   |                           |                           |  |

|---------|----------------------------------|-----|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|----------------------------------|----|---|---------------------------|---------------------------|--|

| 81-95   | C <sub>0</sub> -C <sub>14</sub>  | 0   | <ul> <li>Common ou</li> <li>Segment ou</li> <li>Common Ou</li> <li>Following of<br/>alternating(</li> </ul> | <ul> <li>CD driving signal output terminals.</li> <li>Common output terminals :C<sub>0</sub> to C<sub>24</sub></li> <li>Segment output terminals :S<sub>0</sub> to S<sub>99</sub></li> <li>Common Output Terminal<br/>Following output voltages is selected by the conditional data.</li> </ul> |                                   |                                  |    |   |                           |                           |  |

| 98-197  | S <sub>0</sub> -S <sub>99</sub>  | 0   | Scan data                                                                                                   | FR<br>H                                                                                                                                                                                                                                                                                         | Output Voltag<br>V <sub>5</sub>   | je                               |    |   |                           |                           |  |

|         | 0 00                             |     | Н                                                                                                           | L                                                                                                                                                                                                                                                                                               | V <sub>DD</sub>                   |                                  |    |   |                           |                           |  |

|         |                                  |     | L                                                                                                           | Н                                                                                                                                                                                                                                                                                               | V <sub>1</sub>                    |                                  |    |   |                           |                           |  |

|         |                                  |     |                                                                                                             | L                                                                                                                                                                                                                                                                                               | V <sub>4</sub>                    |                                  |    |   |                           |                           |  |

|         |                                  |     | <ul> <li>Segment out<br/>Following<br/>alternating(</li> </ul>                                              | put terminal<br>output voltages is<br>FR) signal and dis                                                                                                                                                                                                                                        | play data in the                  | DD RAM.                          | of |   |                           |                           |  |

| 200-209 | C <sub>24</sub> -C <sub>15</sub> | 0   | RAM data                                                                                                    | FR                                                                                                                                                                                                                                                                                              |                                   | t Voltage                        |    |   |                           |                           |  |

|         |                                  |     |                                                                                                             |                                                                                                                                                                                                                                                                                                 |                                   |                                  |    | Н | Normal<br>V <sub>DD</sub> | Reverse<br>V <sub>2</sub> |  |

|         |                                  |     | Н                                                                                                           |                                                                                                                                                                                                                                                                                                 | V <sub>DD</sub><br>V <sub>5</sub> | V <sub>2</sub><br>V <sub>3</sub> |    |   |                           |                           |  |

|         |                                  |     |                                                                                                             | н                                                                                                                                                                                                                                                                                               | V <sub>2</sub>                    | V <sub>DD</sub>                  |    |   |                           |                           |  |

|         |                                  |     |                                                                                                             | L                                                                                                                                                                                                                                                                                               | V <sub>3</sub>                    | V <sub>5</sub>                   |    |   |                           |                           |  |

| 19      | DUTY                             |     | Duty and Bias sel                                                                                           | ection terminal.                                                                                                                                                                                                                                                                                |                                   |                                  |    |   |                           |                           |  |

| _       |                                  |     | DUTY                                                                                                        | Duty                                                                                                                                                                                                                                                                                            | Bias                              | 7                                |    |   |                           |                           |  |

|         |                                  |     | Н                                                                                                           | 1/15                                                                                                                                                                                                                                                                                            | 1/5                               |                                  |    |   |                           |                           |  |

|         |                                  |     | L                                                                                                           | 1/25                                                                                                                                                                                                                                                                                            | 1/6                               |                                  |    |   |                           |                           |  |

| 20      | CDIR                             | 1   | Common Driver A                                                                                             | ssignment selection                                                                                                                                                                                                                                                                             |                                   |                                  |    |   |                           |                           |  |

|         |                                  |     | H                                                                                                           | Reverse (C <sub>24</sub>                                                                                                                                                                                                                                                                        |                                   |                                  |    |   |                           |                           |  |

|         |                                  |     | L                                                                                                           | Normal ( $C_{0}$                                                                                                                                                                                                                                                                                |                                   |                                  |    |   |                           |                           |  |

|         |                                  |     |                                                                                                             | ( 0                                                                                                                                                                                                                                                                                             | /                                 |                                  |    |   |                           |                           |  |

# ■ FUNCTIONAL DESCRIPTION

#### (1) Description for each blocks

(1-1) Busy Flag (BF)

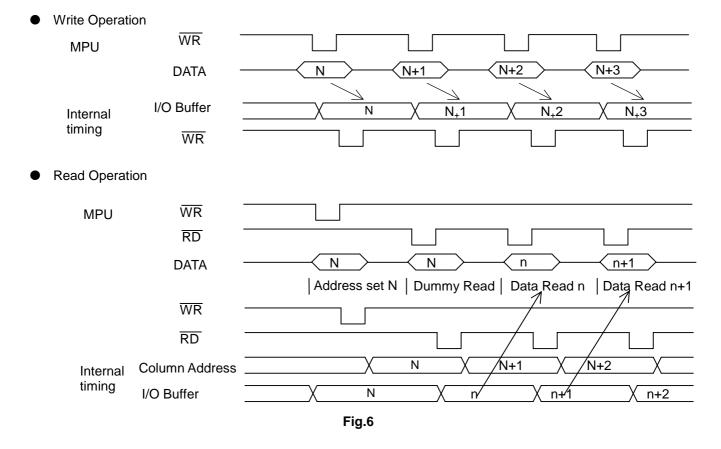

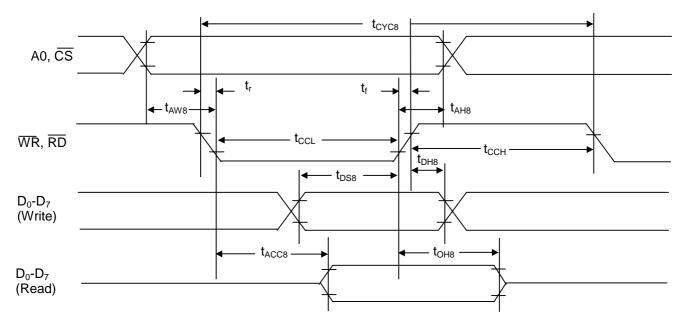

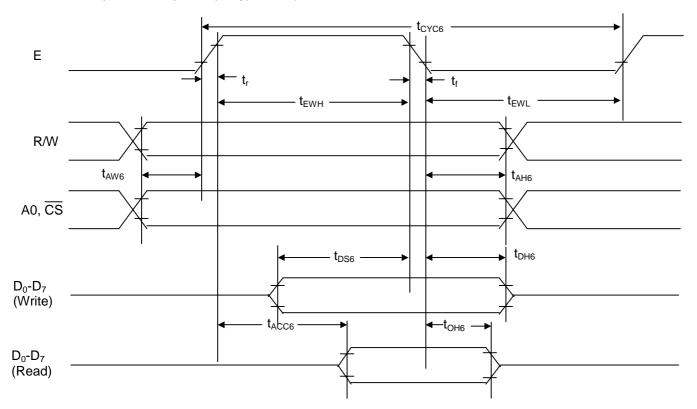

The Busy Flag (BF) is set to logical "1" in busy of internal execution by an instruction, and any instruction excepting for the "Status Read" is disable at this time. Busy Flag is outputted through  $D_7$  terminal by "Status Read" instruction. Although another instructions should be inputted after check of Busy Flag, no need to check Busy flag if the system cycle time ( $t_{CYC}$ ) as shown in **BUS** TIMING CHARACTERISTICS is secured completely.

#### (1-2) Display Start Line Register

The Display Start Line Register is a register to set a display data RAM address corresponding to the COM<sub>0</sub> display line (the top line normally) for the vertical scroll on the LCD, Page address change and so forth. The Display Start Line Address set instruction sets the 8-bit display start address into this register.

#### (1-3) Line Counter

Line Counter is reset when the internal FR signal is switched and outputs the line address of the display data RAM by count up operation synchronizing with common cycle of **NJU6673**.

#### (1-4) Column Address Counter

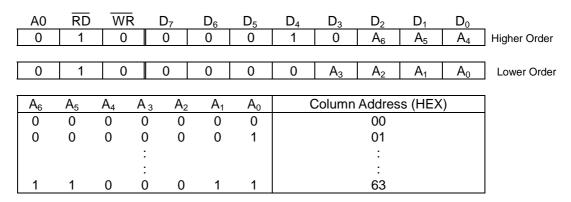

Column Address Counter is the 8-bit preset-able counter to point the column address of the display data RAM (DD RAM) as shown in Fig. 1. The counter is incremented automatically after the display data read/write instructions execution. When the Column address counter reaches to the maximum existing address by the increment operations, the count up operation (increment) is frozen. However, when new address is set to the column address counter again, it restarts the count up operation from a set address. The operation of Column Address Counter is independent against Page Address Register.

By the address inverse instruction (ADC select) as shown in Fig. 1, Column Address Decoder reverses the correspondence between Column address and Segment output of display data RAM.

#### (1-5) Page Address Register

Page Address Register assigns the page address of the display data RAM as shown in Fig. 1. In case of accessing from the MPU with changing the page address, Page Address Set instruction is required.

#### (1-6) Display Data RAM

The Display data RAM (DD RAM) is the bit map RAM consisting of 2,500 bits to store the display data corresponding to the LCD pixel on LCD panel.

In Normal Display : "1" Turn-On Display, "0"=Turn-Off Display In Reveres Display: "1" Turn-Off Display, "0"=Turn-On Display

DD RAM output 100 bits parallel data addressed by line address counter then the data latched in the display data latch. Asynchronous data access to the DD RAM is available due to the access to the DD RAM from the MPU and latch to the display data latch operation are done independently.

#### (1-7) Common Driver Assignment

The scanning order can be assigned by set Common Driver Assignment selection terminal as shown on Table 1.

|                       |          |                         | <u> </u>          |             |                         |                   |

|-----------------------|----------|-------------------------|-------------------|-------------|-------------------------|-------------------|

|                       |          |                         | COM               | Dutputs Ter | minals                  |                   |

|                       | PAD No.  | 81                      | 95                |             | 200                     | 209               |

|                       | Pin name | C <sub>0</sub>          | C <sub>14</sub>   |             | C <sub>24</sub>         | C <sub>15</sub>   |

| COM Driver Assignment | "L"      | $COM_0 \longrightarrow$ | COM <sub>14</sub> |             | COM <sub>24</sub> -     | COM <sub>15</sub> |

| selection terminal    | "H"      | COM <sub>24</sub>       | COM <sub>10</sub> |             | $COM_0 \longrightarrow$ | COM <sub>9</sub>  |

#### Table 1 Common Driver Order Assignment

The duty ratio setting and output assignment register are so controlled to operate independently that duty ratio setting required to corresponding duty ratio for output assignment.

| Page<br>Address                        | Data                             |       |       |       |       | Dis   | play                  | Pattern    |                 |                 | Line<br>Address |   | COM out<br>example                 |                 |

|----------------------------------------|----------------------------------|-------|-------|-------|-------|-------|-----------------------|------------|-----------------|-----------------|-----------------|---|------------------------------------|-----------------|

| Address                                | D <sub>0</sub>                   |       |       |       |       |       |                       |            |                 |                 | 00              | 1 | C <sub>17</sub>                    | 1               |

|                                        | $D_0$<br>$D_1$                   |       |       |       |       |       |                       |            |                 |                 | 00              | - | C <sub>17</sub><br>C <sub>18</sub> |                 |

| -                                      | D <sub>1</sub><br>D <sub>2</sub> |       |       |       |       |       |                       | <u> </u>   |                 |                 | 01              | ŀ | C <sub>19</sub>                    | -               |

| $D_1, D_0$                             | D <sub>2</sub><br>D <sub>3</sub> |       |       |       |       |       |                       |            |                 |                 | 02              | ŀ | C <sub>20</sub>                    | -               |

| (0, 0)                                 | D <sub>3</sub>                   |       |       |       |       |       |                       | — Page 0 — |                 |                 | 00              | ŀ | C <sub>21</sub>                    |                 |

| (-, -)                                 | D <sub>5</sub>                   |       | -     |       |       |       |                       |            |                 |                 | 05              | F | C <sub>22</sub>                    | СОМ             |

| -                                      | D <sub>6</sub>                   |       |       |       |       |       |                       |            |                 |                 | 06              | ŀ | C <sub>23</sub>                    | output          |

|                                        | D <sub>7</sub>                   |       |       |       |       |       |                       |            |                 |                 | 07              | ľ | C <sub>24</sub>                    | example 2       |

|                                        | D <sub>0</sub>                   |       |       |       |       |       |                       |            |                 |                 | 08              | Ī |                                    | C <sub>0</sub>  |

|                                        | D <sub>1</sub>                   |       |       |       |       |       |                       |            |                 |                 | 09              | ľ | C <sub>1</sub>                     | C <sub>1</sub>  |

|                                        | D <sub>2</sub>                   |       |       |       |       |       |                       |            |                 |                 | 0A              | Ī | C <sub>2</sub>                     | C <sub>2</sub>  |

| D <sub>1</sub> , D <sub>0</sub>        | $D_3$                            |       |       |       |       |       |                       | — Page 1 — |                 |                 | 0B              | Ī | C <sub>3</sub>                     | C <sub>3</sub>  |

| (0, 1)                                 | $D_4$                            |       |       |       |       |       |                       |            |                 |                 | 0C              | [ | $C_4$                              | C <sub>4</sub>  |

|                                        | $D_5$                            |       |       |       |       |       |                       |            |                 |                 | 0D              | [ | C <sub>5</sub>                     | C <sub>5</sub>  |

|                                        | $D_6$                            |       |       |       |       |       |                       |            |                 |                 | 0E              |   | $C_6$                              | C <sub>6</sub>  |

|                                        | $D_7$                            |       |       |       |       |       |                       |            |                 |                 | 0F              |   | C <sub>7</sub>                     | C <sub>7</sub>  |

|                                        | $D_0$                            |       |       |       |       |       |                       |            |                 |                 | 10              |   | C <sub>8</sub>                     | C <sub>8</sub>  |

|                                        | D <sub>1</sub>                   |       |       |       |       |       |                       |            |                 |                 | 11              |   | C <sub>9</sub>                     | C <sub>9</sub>  |

|                                        | $D_2$                            |       |       |       |       |       |                       |            |                 |                 | 12              |   | C <sub>10</sub>                    | C <sub>10</sub> |

| $D_1, D_0$                             | $D_3$                            |       |       |       |       |       |                       | — Page 2 — |                 |                 | 13              |   | C <sub>11</sub>                    | C <sub>11</sub> |

| (1, 0)                                 | $D_4$                            |       |       |       |       |       |                       |            |                 |                 | 14              | _ | C <sub>12</sub>                    | C <sub>12</sub> |

|                                        | $D_5$                            |       |       |       |       |       |                       |            |                 |                 | 15              |   | C <sub>13</sub>                    | C <sub>13</sub> |

|                                        | D <sub>6</sub>                   |       |       |       |       |       |                       |            |                 |                 | 16              | _ | C <sub>14</sub>                    | C <sub>14</sub> |

|                                        | $D_7$                            |       |       |       |       |       |                       |            |                 |                 | 17              | - | C <sub>15</sub>                    | -               |

| D <sub>1</sub> , D <sub>0</sub> (1, 1) | D <sub>0</sub>                   |       |       |       |       |       |                       | Page 3     |                 |                 | 18              | L | C <sub>16</sub>                    |                 |

| Column                                 | D <sub>0</sub> =0                | 00    | 01    | 02    | 03    | 04    | 05                    | •••••      | 62              | 63              |                 |   |                                    |                 |

| Address(ADC                            | 5) D <sub>0</sub> =1             | 63    | 62    | 61    | 60    | 5F    | 5E                    | •••••      | 01              | 00              |                 |   |                                    |                 |

|                                        |                                  |       |       |       |       |       |                       |            |                 |                 | Ì               |   |                                    |                 |

| Segmer                                 | nt output                        | $S_0$ | $S_1$ | $S_2$ | $S_3$ | $S_4$ | <b>S</b> <sub>5</sub> | •••••      | S <sub>98</sub> | S <sub>99</sub> |                 |   |                                    |                 |

COM output example1 : 1/25Duty, set Display Start Line  $08_H$  COM output example2 : 1/15Duty, set Display Start Line  $08_H$

# Fig.1 Correspondence with Display Data RAM Address

# (1-8) Reset Circuit Reset circuit operates the following initializations when the condition of RES terminal goes to "L" level.

#### Initialization

- 1. Display Off

- 2. Normal Display (Non-inverse display)

- 3. ADC Select : Normal (ADC Instruction D<sub>0</sub>="0")

- 4. Read Modify Write Mode Off

- 5. Voltage Booster off, Voltage Regulator off, Voltage follower off

- 6. Clear the serial interface register

- 7. Driver Output Off

- 8. Set the Display Start Line Register to 00<sub>H</sub>

- 9. Set the Column Address Counter to 00<sub>H</sub>

- 10. Set the Page Address Register to page "0"

- 11. Set the EVR register to  $00_H$

The  $\overline{\text{RES}}$  terminal connects to the reset terminal of the MPU synchronization with the MPU initialization as shown in "the MPU interface" in the Application Circuit section. The "L" level input signal as reset signal must keep the period over than 10µs as shown in DC Characteristics. The **NJU6673** takes 1µs for the reset operation after the rising edge of the  $\overline{\text{RES}}$  signal.

The reset operation by  $\overline{\text{RES}}$  ="L" initializes each resister setting as above reset status, but the internal oscillation circuit and output terminals (D<sub>0</sub> to D<sub>7</sub>) are not affected.

To avoid the lock-up, the reset operation by the RES terminal must be required every time when power terns on. The reset operation by the reset instruction, function 8 to 11 operations mentioned above is performed.

The RES terminal must be keep "L" level when the power terns on in not use of the built-in LCD power supply circuit for no affect to the internal execution.

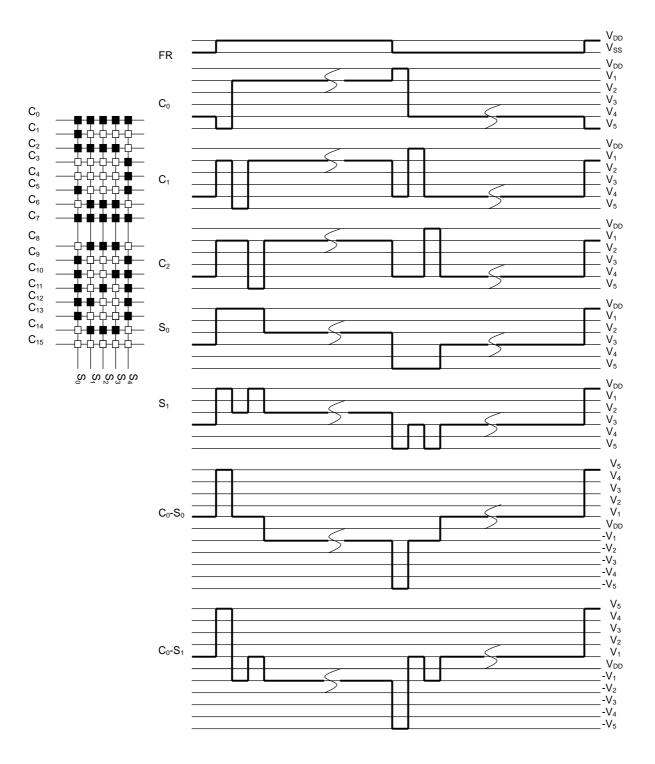

#### (1-9) LCD Driving

(a) LCD Driving Circuits

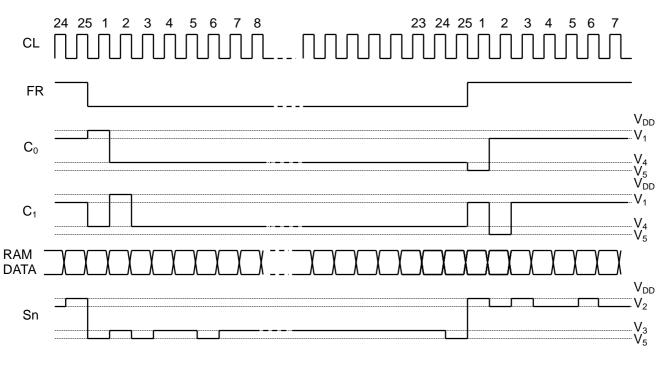

LCD driver is 125 sets of multiplexer consisting of 100 segments and 25 commons drivers to output LCD driving voltage. The common driver outputs the common scan signals formed with the shift register. The segment driver outputs the segment driving signal determined by a combination of display data in the DD RAM, common timing, FR signal, and alternating signal for LCD. The output wave forms of segment/common are shown in ■ LCD DRIVING WAVEFORM.

(b) Display Data Latch Circuits

Display Data Latch Circuit latches the 100 bits display data outputted from the DD RAM addressed by the Line address counter to LCD driver at every common signal cycle temporarily. The original data in the DD RAM is not changed because of the Normal/Reverse display, Display On/Off, Static drive On/Off instruction processes only stored data in this Display Data Latch Circuit.

#### (c) Line Counter and Latch signal of Latch Circuits

The count clock to Line Counter and the latch clock to Display Data Latch Circuit are formed using the internal display clock (CL). The display data of 100 bits from Display Data RAM pointed by the line address synchronizing with the internal display clock are latched into the Display Data Latch Circuit and are outputted to LCD driving circuits.

The display data read out operation from DD RAM to the LCD Driver Circuit is completely independent operation with an access to the display data RAM from MPU.

New Japan Radio Co., Ltd.

(d) Display Timing Generaton Circuit

The display timing generation circuit generates the internal timing of the display system by the master clock and the internal FR signal. As for it, the internal FR signal and the LCD alternating signal generate the wave form of 2-frame alternating drive wave form or the n-line inverse drive method for the LCD Driving circuit.

# (e) Common Timing Generation

The Common Timing Generator generates the common timing signal from the display clock (CL).

Fig. 2

#### (f) Oscillation Circuit

The Oscillation Circuit is a low power type CR oscillator using an internal resistor and capacitor. The oscillator output is using for the display timing clock and for the voltage booster circuit. And the display clock(CL) is generated from this oscillator output frequency by dividing.

|        | –    |      |

|--------|------|------|

| Duty   | 1/15 | 1/25 |

| Divide | 1/10 | 1/6  |

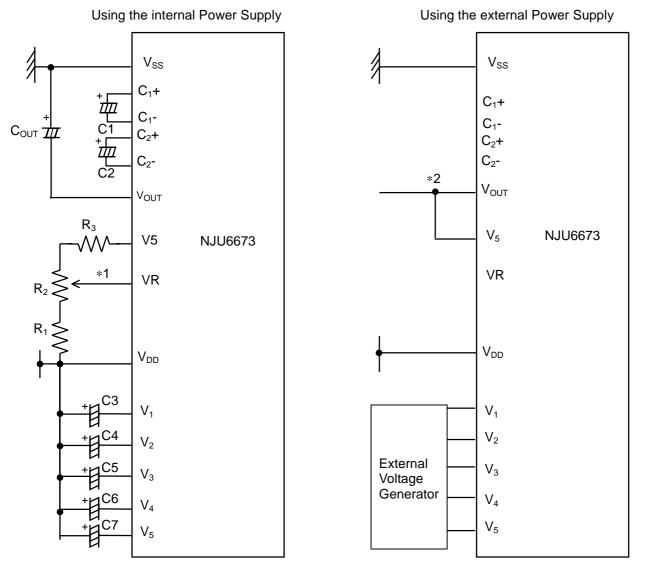

# (g) Power Supply Circuit

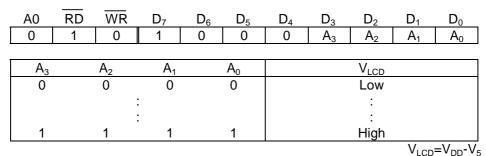

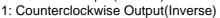

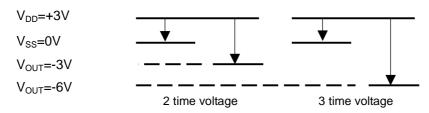

The internal power supply circuit generates the voltage for driving LCD. It consists of voltage booster circuits (3-Time maximum), voltage regulator circuits, and voltage followers.

The operation of internal Power Supply Circuits is controlled by the Internal Power Supply On/Off Instruction. When the Internal Power Supply Off Instruction is executed, all of the voltage booster circuits, regulator circuits, voltage follower circuits are turned off. In this time, the bias voltage of V<sub>1</sub>, V<sub>2</sub>, V<sub>3</sub>, V<sub>4</sub>, V<sub>5</sub> and V<sub>OUT</sub> for the LCD should be supplied from outside, terminals C<sub>1</sub>+, C<sub>1</sub>-, C<sub>2</sub>+, C<sub>2</sub>- and VR should be open. The status of internal power supply is selected by T<sub>1</sub> and T<sub>2</sub> terminals. Furthermore the external power supply operates with some of internal power supply function.

|                | Table          | 5 THE Keld         | LION Delween | ower Suppry |                                   |                                                                           |          |

|----------------|----------------|--------------------|--------------|-------------|-----------------------------------|---------------------------------------------------------------------------|----------|

| T <sub>1</sub> | T <sub>2</sub> | Voltage<br>Booster | Voltage Adj. | Buffer(V/F) | Ext.Power<br>Supply               | C <sub>1</sub> +, C <sub>1</sub> -,<br>C <sub>2</sub> +, C <sub>2</sub> - | VR Term. |

| L              | L/H            | ON                 | ON           | ON          | -                                 |                                                                           |          |

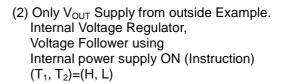

| Н              | L              | OFF                | ON           | ON          | V <sub>OUT</sub>                  | Open                                                                      |          |

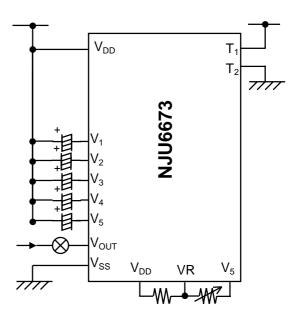

| Н              | Н              | OFF                | OFF          | ON          | V <sub>5</sub> , V <sub>OUT</sub> | Open                                                                      | Open     |

| Table3 | The Relation Between Power Supply Circuit And T <sub>1</sub> , T <sub>2</sub> Terminal |

|--------|----------------------------------------------------------------------------------------|

|--------|----------------------------------------------------------------------------------------|

When  $(T_1, T_2)=(H, L)$ ,  $C_1+$ ,  $C_1-$ ,  $C_2+$ ,  $C_2-$  terminals for voltage booster circuits are open because the voltage booster circuits doesn't operate. Therefore LCD driving voltage to the V<sub>OUT</sub> terminal should be supplied from outside.

When  $(T_1, T_2)=(H, H)$ , terminals for voltage booster circuits and VR are open, because the voltage booster circuits and Voltage adjust circuits do not operate.

The internal power supply Circuits is designed specially for a small-size LCD like as normal cellular phone size LCD panel. When **NJU6673** apply to the large size LCD panel application (large capacitive load), external power supply is required to keep good display condition.

The external capacitors to  $V_1$  to  $V_5$  for Bias voltage stabilization may be removed in use of small size LCD panel. The equivalent load of LCD panel may be changed depending on display patterns. Therefore, it require display quality check on various display patterns actually without external capacitors. If the display quality is not so good, external capacitors should connects as show in (3-4)LCD Driving Voltage Generation Circuits -Fig. 4. (If no need external capacitors as result of experiment, the application patterns (wiring) should be prepared for recovery.)

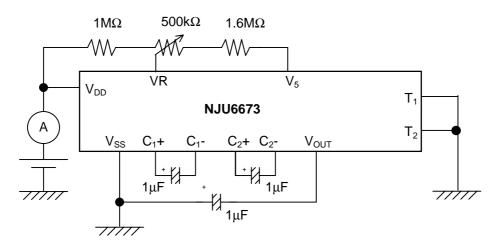

# **O Power Supply applications**

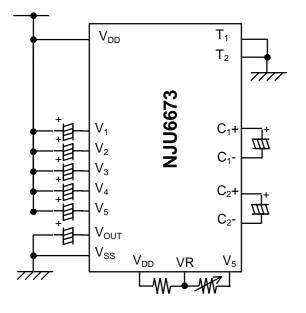

(1) Internal power supply example.

All of the Internal Booster, Voltage Regulator, Voltage Follower using.

Internal power supply ON (instruction) (T<sub>1</sub>, T<sub>2</sub>)=(L, L)

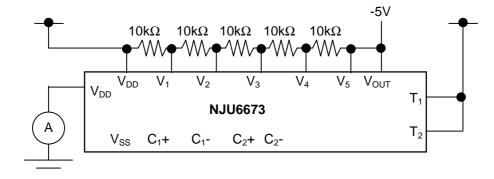

(3)  $V_{OUT}$  and  $V_5$  supply from outside Example. Internal Voltage Follower using. Internal power supply (Instruction)  $(T_1, T_2)=(H, H)$

(4) External Power Supply Example. All of V<sub>1</sub> to V<sub>5</sub> and V<sub>OUT</sub> supply from outside Internal power supply (Instruction)  $(T_1, T_2)=(H, H)$

$\bigotimes$ : These switches should be open during the power save mode.

# (2) Instruction

The **NJU6673** distinguishes the signal on the data bus  $D_0$  to  $D_7$  as an Instruction by combination of A0, RD and WR(R/W). The decode of the instruction and execution performs with only high speed Internal timing without relation to the external clock. Therefore no busy flag check required normally. In case of serial interface, the data input as MSB(D<sub>7</sub>) first serially. The Table. 4 shows the instruction codes of the **NJU6673**.

|     |                                         |        |        |        |                |        | Code           | د                   |        |        |                    |             | ( .Doint Care)                                                                      |

|-----|-----------------------------------------|--------|--------|--------|----------------|--------|----------------|---------------------|--------|--------|--------------------|-------------|-------------------------------------------------------------------------------------|

|     | Instruction                             | A0     | RD     | WR     | D <sub>7</sub> | $D_6$  | D <sub>5</sub> | _<br>D <sub>4</sub> | $D_3$  | $D_2$  | $D_1$              | $D_0$       | Description                                                                         |

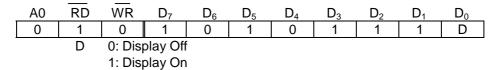

| (a) | Display ON/OFF                          | 0      | 1      | 0      | 1              | 0      | 1              | 0                   | 1      | 1      | 1                  | 0/1         | LCD Display ON/OFF<br>D <sub>0</sub> =0:OFF D <sub>0</sub> =1:ON                    |

| (b) | Display Start<br>Line Set               | 0      | 1      | 0      | 0              | 1      | *              |                     | Star   | t adc  | lress              |             | Determine the Display Line of RAM to COM $_{\rm 0}$                                 |

| (c) | Page Address Set                        | 0      | 1      | 0      | 1              | 0      | 1              | 1                   | *      | *      |                    | age<br>ress | Set the page of DD RAM to the<br>Page Address Register                              |

|     | Column Address Set<br>High Order 3bits  | 0      | 1      | 0      | 0              | 0      | 0              | 1                   | 0      | 0      | gh O<br>Colum      | n           | Set the Higher order 3 bits<br>Column Address to the Reg.                           |

| (d) | Column Address Set<br>Lower Order 4bits | 0      | 1      | 0      | 0              | 0      | 0              | 0                   |        |        | er Order<br>mn Add |             | Set the Lower order 4 bits<br>Column Address to the Reg.                            |

| (e) | Status Read                             | 0      | 0      | 1      |                | Sta    | tus            |                     | 0      | 0      | 0 0                |             | Read out the internal Status                                                        |

| (f) | Write Display Data                      | 1      | 1      | 0      |                |        | ,              | Write               | e Dat  | а      |                    |             | Write the data into the Display<br>Data RAM                                         |

| (g) | Read Display Data                       | 1      | 0      | 1      |                |        |                | Read                | l Dat  | а      |                    |             | Read the data from the Display Data RAM                                             |

| (h) | Normal or Inverse of<br>ON/OFF Set      | 0      | 1      | 0      | 1              | 0      | 1              | 0                   | 0      | 1      | 1                  | 0/1         | Inverse the ON and OFF<br>Display                                                   |

| (i) | Static Drive ON<br>/Normal Display      | 0      | 1      | 0      | 1              | 0      | 1              | 0                   | 0      | 1      | 0                  | 0/1         | Whole Display Turns ON $D_0=0$ : Normal $D_0=1$ : Whole Disp. ON                    |

| (j) | EVR Register Set                        | 0      | 1      | 0      | 1              | 0      | 0              | 0                   | S      | Settin | g Da               | ta          | Set the $V_{\text{5}}$ output level to the EVR register                             |

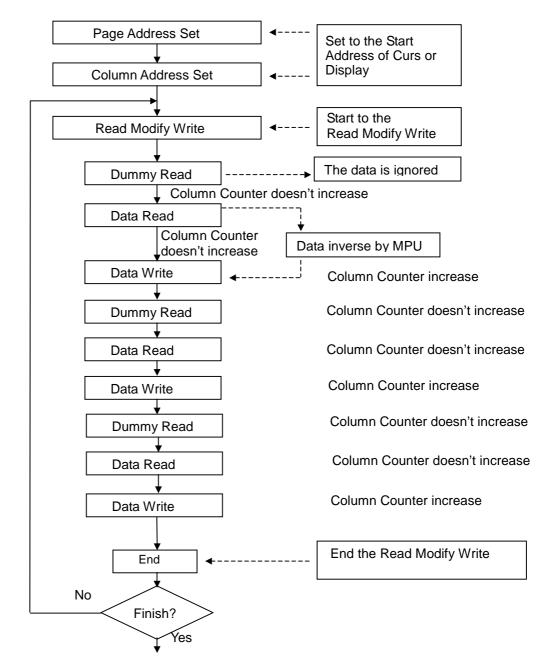

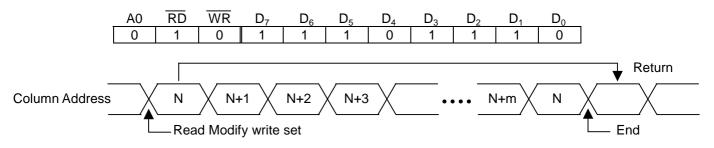

| (k) | Read Modify Write                       | 0      | 1      | 0      | 1              | 1      | 1              | 0                   | 0      | 0      | 0                  | 0           | Increment the Column Address<br>Register when writing but<br>no-change when reading |

| (I) | End                                     | 0      | 1      | 0      | 1              | 1      | 1              | 0                   | 1      | 1      | 1                  | 0           | Release from the Read Modify write Mode                                             |

| (m) | Reset                                   | 0      | 1      | 0      | 1              | 1      | 1              | 0                   | 0      | 0      | 1                  | 0           | Initialize the Internal Circuits                                                    |

| (n) | Internal Power<br>Supply ON/OFF         | 0      | 1      | 0      | 0              | 0      | 1              | 0                   | 0      | 1      | 0                  | 0/1         | 0:Int. Power Supply OFF<br>1:Int. Power Supply ON                                   |

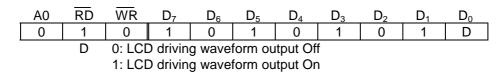

| (o) | Driver Outputs<br>ON/OFF                | 0      | 1      | 0      | 1              | 0      | 1              | 0                   | 1      | 0      | 1 0/1              |             | $D_0=0$ : LCD Driver Outputs OFF $D_0=1$ : LCD Driver Outputs ON                    |

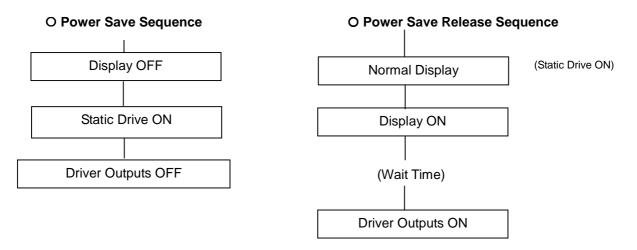

| (p) | Power Save<br>(Complex command)         | 0<br>0 | 1<br>1 | 0<br>0 | 1<br>1         | 0<br>0 | 1<br>1         | 0<br>0              | 1<br>0 |        |                    |             | Set the Power Save Mode<br>(LCD Display OFF + Static<br>Drive ON)                   |

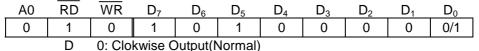

| (q) | ADC Select                              | 0      | 1      | 0      | 1              | 0      | 1              | 0                   | 0      | 0      | 0                  | 0/1         | Set the DD RAM vs Segment $D_0=0$ :Normal $D_0=1$ :Inverse                          |

# Table 4 Instruction Code

(\*:Don't Care)

#### (2-1) Explanation of Instruction Code

# (a) Display On/Off

It executes the On/Off control of the whole display without relation to the DD RAM or any internal conditions.

#### (b) Display Start Line

It sets the DD RAM line address corresponding to the  $COM_0$  terminal (normally assigned to the top display line). In this instruction execution, the display area is automatically set by the lines that correspond to the display duty ratio to the upward direction of the line address. Changing the line address by this instruction performs smooth scrolling to a vertical direction. In this time, the DD RAM data are unchanged.

| A0             | RD             | WR | $D_7$ | $D_6$          | $D_5$          | $D_4$          | $D_3$          | $D_2$          | $D_1$          | D <sub>0</sub> |

|----------------|----------------|----|-------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| 0              | 1              | 0  | 0     | 1              | *              | A <sub>4</sub> | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> |

|                |                |    |       |                |                |                |                |                |                |                |

| A <sub>4</sub> | A <sub>3</sub> | A  | N2    | A <sub>1</sub> | A <sub>0</sub> |                | Line A         | ddress         | (HEX)          |                |

| 0              | 0              | (  | )     | 0              | 0              |                |                | 00             |                |                |

| 0              | 0              | (  | )     | 0              | 1              |                |                | 01             |                |                |

|                |                | :  |       |                |                |                |                | :              |                |                |

|                |                | :  | :     |                |                |                |                | :              |                |                |

| 1              | 1              | (  | )     | 0              | 0              |                |                | 18             |                |                |

#### (c) Page Address Set

When MPU accesses to the DD RAM, a page address is set by page Address Set instruction before writing the data (Note:the change of page address is not affected to the display).

| ] | A0<br>0 | RD<br>1             | WR<br>0 | D <sub>7</sub><br>1 | D <sub>6</sub><br>0 | D <sub>5</sub> | D <sub>4</sub><br>1 | D <sub>3</sub><br>* | D <sub>2</sub><br>* | D <sub>1</sub><br>A <sub>1</sub> | D <sub>0</sub><br>A <sub>0</sub> | *:Don't Care |

|---|---------|---------------------|---------|---------------------|---------------------|----------------|---------------------|---------------------|---------------------|----------------------------------|----------------------------------|--------------|

|   |         | A <sub>1</sub><br>0 |         |                     | A <sub>0</sub><br>0 |                |                     |                     | Page<br>0           |                                  |                                  |              |

|   |         | 0                   |         |                     | 1                   |                |                     |                     | 1                   |                                  |                                  |              |

|   |         | 1                   |         |                     | 0                   |                |                     |                     | 2                   |                                  |                                  |              |